Code: Alles auswählen

MIPS-Architektur

lb, lbu Laden eines Bytes

sb Speichern eines Bytes

lh, lhu Laden eine Halbwortes

sh Speichern eines Halbwortes

lw Laden eines Wortes

sw Speicher eines Wortes

ld* Laden eines Doppelwortes

sd* Speichern eines Doppelwortes

la* Laden einer Addresse

li* Laden eines immidiate Wertes

l.s*, l.d* Laden eines Gleitkommaregisters

s.s*, s.d* Speichern eines Gleitkommaregisters

move* Transfer zwischen Universalregistern

mov.s* Transfer zwischen Gleitkommaregistern

mov.d*

mfhi Transfer zwischen Universalregister und den Regiestern Hi und Lo

mflo

mthi

mtlo

mfc1 Transfer zwischen Universalregistern und Gleitkommaregistern

mtc1

addi Addition

addi

addu

addiu

sub Subtration

sub

mult Multiplikation

multu

div Division

divu

abs* Absoluter Wert

neg* Negation

rem* Modulo

not* Logisches NOT

and Logisches UND

andi

or Logisches OR

ori

xor Logisches XOR

xori

nor Logisches NOR

sll Logisches Linksschieben

sllv

srl Logischse Rechtsschieben

srlv

sra Arithmetische Rechtsverschiebung

srav

rol* Rotation links

ror* Rotation rechts

slt Vergleich kleiner

slti

sltu

stliu

seq* Vergleich gleich

sne* Vergleich ungleich

sgt* Vergleich groesser

sgtu*

sge* Vergleich groeser gleich

sgeu*

sle* Vergleich kleiner gleich

sleu*

j, unbedingter Sprung

b*

jr

jal* Jump mit Speicherung PC+4

jalr Jump Regeister

beq Verzweigung falls gleich

bne Verzweigung falls ungleich

beqz* Verzweigung falls gleich

bnez* Verzweigung falls gleich

bgt* Verzweigung falls groesser

bge* Verzweigung falls groesser gleich

bgtz Verzweigung fals groesser

bgez Verzweigung falls groesser gleich

blt* Verzweigung falls kleiner

ble* Verzweigung falls kleiner gleich

bltz Verzweigung falls kleiner

blez Verzweigung falls kleiner gleich

nop Nulloperation, leere Anweisung

bge*

Befehlssatz = Instruction Set

Befehlsarten:

1. Datenbewegungsbefehle (Data Movement)

2. Arithmetisch-Logische Befehle (Integer Arithmeic and Logical)

3. Schiebe- und Rotationsbefehle (Shift, Rotate)

4. Multimediabefehle

5. Gleitkommabefehle (Floating-Point Instructions)

6. Programmsteuerbefehle (Control Transfer Instructions)

7. Systemsteuerbefehle (System Control Instructions)

8. Synchronisationsbefehle

Gleitkommabefehle (Floating-Point Instructions)

1. Bitfeldorientierte Multimediabefehle

2. Graphikorientierte Multimediabefehle

Datenbewegungsbefehle, auch: push, pop

Saturationsarithmetik: Zahlenüberschreitungen werden auf die höchstwertigste bzw. niederwertigste Zahl abgebildet

Befehlsformate:

Opcode

Dreiaddressformat

Zweiaddressformat

Einaddressformat

Nulladdressformat

Lade/- und Speicherarchitektur (Load/Store Architecture)

Register-Speicher-Architektur

Speicher-Speicher-Architektur

Akkumalatoren-Architekturen

Stack- und Kellerarchitektur

Stackarchiktur: 8087, Intel

ATAM862 Atmel

Addressierungsarten:

Register und Unmittelbare Addressierungsarten

Klasse des Einstufigen Addressierung

Klasse der zweistufigen Addressierung

Datenaddressierung

Registeraddressierung

Unmittelbare Addressierung

Direkte oder absolute Addressierung

Registerindirekte ADdressierung

Registeraddressiernug mit Autoinkrement/Dekrement

Präinkrement, Postinkrement

Prädekrement, Postdekrement

Registerindirekte Addressierung mit Verschiebung (Displacement)

Indizierte Addressierung

Indizierte Addressierung mit Verschiebung

Befehlsaddressierung

Befehlsrelativer Modus

Befehlszählerindirekt

+++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++

- Big-Endian-Format

- Little-Endian-Format

- Datenformate

1. Einzelbit

2. Ganzzahl (Integer)

3. Gleitkomma

4. Multimedia

Ganzzahldatenformate:

- signed

- unsigned

- packed

- unpacked

- BCD-Zahlen (Binary Coded Decimals)

- ASCII

Bate

Halbwort

Wort

Doppelwort

Gleitkommadatenformate (IEEE-754-Standard)

Einfache Genauigkeit: 32 Bit

Doppelte Genauigkeit: 64 Bit

Erweiterte Genauigkeit: 80 Bit

f = (-1)^s * 1.m*2^(e-b)

biased - verschoben

b bias

m Mantissenanteil

b = 2^{ne-1}-1

p = 23, einfache

p = 52, doppelte

p = 63, erweiterte

Multimediaformate: 64 Bit breite Wörter

Bitfeldorientierte

Graphikorientierte

Befehlssatz

Datenbwegungsbefehle (Data Movement)

Arithmetisch-Logische-Befehle

Schiebe- und Rotationsbefehle

Multmediabefehle

Gleitkommabefehle

Programmsteuerbefehle

Systemsteuerbefehle

Synchronisationsbefehle

SWAP, TAS

Befehlsformate (instruction format)

Dreiaddressformat (3-Address Instruction Format), zwei Quelloperanden, ein Zieloperand

Zweiaddressformat

Einaddressformat

Nulladdressformat

Lade-/Speicherarchitektur (Load/Store Architecture)

Register-Register-Architektur

Register-Speicher-Architektur

Speicher-Speicher-Architektur

Akkumalatorarchitektur

Stack- oder Kellerarchitektur

Addressierungsart

Effektive Addresse

Effektive Addresse

Virtuelle Addresse

Physikalische Addresse

Datenaddressierungsarten

Registeraddressierung

Unmittelbare Addressierung

Direkte oder absolute Addressierung

Registerindirekte Addressierung

Registerindirekte Addressierung mit Autoinkrement/Autodekrement

Präinkrement, Postinkrement, Prädekrement, Postdekrement

Registerindirekte Addressierung mit Verschiebung (Displacement)

Indizierte Addressierung

Indizierte Addressierung mit Verschiebung

Befehlsaddressierungsarten

Befehlsrelativer Modus

Befehlsindirekter Modus

MIS Register

$0 bis $31

$0 $zero 0 (read-only)

$1 $at reserviert für den Assembler

$2 - $3 $v0 - $v1 Rückgabewert von Funktionsaufrufen

$4 - $7 $a0 - $a3 Argumente für den Funktionsauf

$8 - $15 $t0 - $t7 Temporäre Variablen

$16 - $23 $s0 - $s7 Gesicherte Variablen

$24 - $25 $t8 - $t9 Temporäre Variablen

$26 - $27 $k0 - $k1 Reserviert für das Betriebssystem

$28 $gp Data Segment Pointer

$29 $sp Stack Pointer

$30 $fp Frame Pointer

$31 $ra Return Address

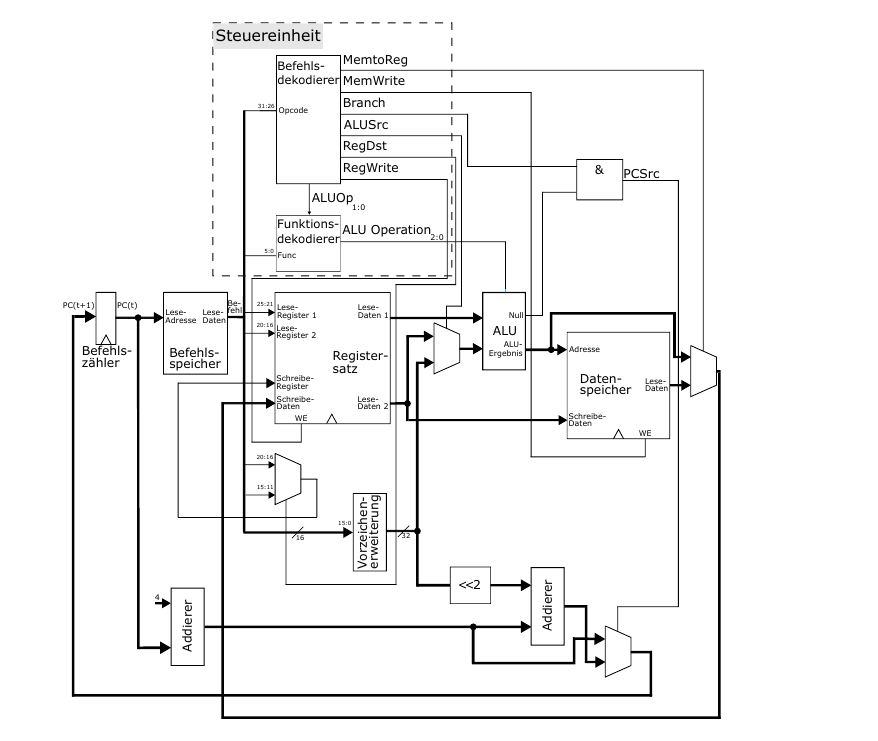

Einzyklus-Mikroarchitekur

Zustandselemente

Zustandselemente:

- PC

- Befehlsspeicher

- Registersatz

- Datenspeicher

Befehlszählerregister

Befehlsspeicher

Datenpfad

Befehlsholephase (Instruction Fetch - IF)

Zustandselmente

1. Befehlszähler

2. Befehlsspeicher

3. Registersatz

4. Datenspeicher

Datenpfade für die Daten (Nicht Befehle):

Also:

- Lesedaten brauchen keinen Eingabeport - warum auch? Aus ihnen wird gelesen

Stattdessen 5-Bit-Addresse (32-Bit-Register)

- Dann haben wir 3-Address-Befehle - also 2 Lesedaten

- Eine Schreibedaten: 32 Bit

- Ein Schreiberegister (Welches - 5 Bit)

- Einen CLK

- Ein WE (Write Enable)

Das ist oder war schon der Registersatz

Danach kommt die ALU und jetzt nicht direkt verbunden mit Registersatz, sondern mit Datenspeicher

Der Befehlsdekodierer bzw. die Steuereinheit hat Steuerleitung zu

- RegWrite - Registersatz - WE

- MemWrite für Datenspeicher

- Keine Daten zu Lese-Daten und Lese-Register, diese sind immer frei

=> Das müssen wir uns so vorstellen, wie mit unseren Multiplexern im Operationswerk

Zunächst mal das Wichtigste:

- Registersatz

- Datenspeicher

- ALU

- Steuereinheit

Der Datenspeicher ist wiederum mit dem Registersatz verbunden

Registersatz -> (Lese-Daten 1, Lese-Daten 2) -> ALU -> Datenspeicher

Multiplexer sind:

1. Vor ALU (Lese Daten 2)/Für Befehle, zum Berechnen der Adresse

2. Nach Datenspeicher: Entweder Datenspeicher oder ALU

Weil: Registersatz -> Datespeicher

Von Datenspeicher oder ALU kann das Ergebnis nach Regsistersatz

Registersatz -> (Lese-Daten 1, Lese-Daten 2) -> ALU/Datenspeicher -> Registersatz

Alles, was mit Befehlen im Operationswerk zu tun hat

1. Befehlszähler

2. Befehlsspeicher

3. Vorzeichenerweiterung

4. 2x Addierer

Register-Satz - Lese-Daten 1 -> ALU -> Datenspeicher -> MUX

Register-Satz - Lese-Daten 1 -> ALU -> MUX

Register-Satz - Lese-Daten 1 -> ALU -> Datenspeicher -> MUX -> Registersatz - Schreibedaten

Register-Satz - Lese-Daten 1 -> ALU -> MUX -> Registersatz - Schreibedaten

Register-Satz - Lese-Daten 2 -> MUX -> ALU -> MUX

Register-Satz - Lese-Daten 2 -> MUX -> ALU -> Datenspeicher -> MUX

Normaler Befehlspfad ohne Verzweifung

Befehlszähler -> Befehlsspeicher

Befehlszähler -> Addierer +4 MUX -> Befehlszähler.

Steuereinheit:

1. Befehlsdekodierer

2. Funktionsdekodierer

Befehlsdekodierer:

1. MemtoReg

2. MemWrite

3. Branch

4. ALUSrc

5. RegDst

6. RegWrite

7. ALUOp

Funktionsdekodierer: ALU Operation: 3 Bit

Funktionsdekodierer:

1. Ausgang: ALU Operation: 3 Bit

2. Eingang: Func - vom Befehl - 6 Bit

3. Eingang: ALUOp, 2 Bit vom Befehlsdekodierer

Befehlsdekodierer

Funktionsdekodierer

Registersatz

ALU

Datenspeicher

Befehlsspeicher

Befehlszähler

Vorzeichenerweiterungseinheit

4 x MUX

1 x AND

2 x Addierer

1 x Bit Shifter

Befehlsdekodierer:

1. MemtoReg

2. MemWrite

3. Branch

4. ALUSrc

5. RegDst

6. RegWrite

7. ALUOp

Funktionsdekodierer:

1. Func

2. ALUOp

3. ALU Operation

Registersatz:

- Lese-Register 1

- Lese-Register 2

- Schreiberegister

- Schreibedaten

- WE

- Lese-Daten 1

- Lese-Daten 2

ALU:

- ALU-Ergebnis

- Null

AND:

- PCSrc

Datenspeicher:

- Addresse

- Schreibedaten

- WE

- Lesedaten

Befehlsspeicher:

- Leseaddresse

- Lesedaten

Befehlszähler:

- PC (t+1)

- PC (t)

Alle Datenwege:

1. MemtoReg (Befehlsdekodierer)

2. MemWrite (Befehlsdekodierer)

3. Branch (Befehlsdekodierer)

4. ALUSrc (Befehlsdekodierer)

5. RegDst (Befehlsdekodierer)

6. RegWrite (Befehlsdekodierer)

7. ALUOp (Befehlsdekodierer)

8. Func (Funktionsdekodierer)

9. ALUOp (Funktionsdekodierer)

10. ALU Operation (Funktionsdekodierer)

11. Lese-Register 1 (Registersatz)

12. Lese-Register 2 (Registersatz)

13. Schreiberegister (Registersatz)

14. Schreibedaten (Registersatz)

15. WE (Registersatz)

16. Lese-Daten 1 (Registersatz)

17. Lese-Daten 2 (Registersatz)

18. ALU-Ergebnis (ALU)

19. Null (ALU)

20. PCSrc (AND)

21. Addresse (Datenspeicher)

22. Schreibedaten (Datenspeicher)

23. WE (Datenspeicher)

24. Lesedaten (Datenspeicher)

25. Leseaddresse (Befehlsspeicher)

26. Lesedaten (Befehlsspeicher)

27. PC (t+1) (Befehlszähler)

28. PC (t) (Befehlszähler)

Abgeschrieben, das war aus dem Blockschaltbild - aber allgemeiner Prozessor (OpenSource - und kann jeder verwenden):

ALUOp Func ALU Operanden

00 X 010 - add

X1 X 110 - sub

1X 100000 - add 010 - add

1X 100010 - sub 110 - sub

1X 100100 - and 000 - and

1X 100101 - or 001 - or

1X 101010 - slt 111 - set les than

Op-Code Reg-Write Reg-Dst ALU-Src Branch Mem-Write Mem-toReg ALU-Op

R-Typ 000000 1 1 0 0 0 0 10

lw 100011 1 0 1 0 0 1 00

sw 101011 0 X 1 0 1 X 00

beq 000100 0 X 0 1 0 X 01

Geographisch, von Süden nach Norden und Westen nach Osten

Addierer, Befehlszähler, Befehlsspeicher

MUX, Registersatz, Funktionsdekodierer, Befehlsdekodierer

Vorzeichenweiterung, Registersatz, Funktionsdekodierer, Befehlsdekodierer

2-Bit-Shifter, MUX, ALU

Addierer, Datenspeicher, AND

Oder als ganze Blöcke, von Westen nach Osten, Süden nach Norden

Block 1:

Addierer, Befehlszähler, Befehlsspeicher

Block 2:

MUX, Vorzeichenerweiterung

Regisersatz

Funktionsdekodierer, Befehlsdekodierer

Block 3

2-Bit-Shifter, Addierer, ALU

MUX, ALU, Datenspeiecher, MUX

AND

Pfade am MIPS Prozessor

Befehlszähler

Eingang: PC (t)

Ausgang: PC (t+1)

Befehlsspeicher:

Eingang: Leseaddresse

Ausgang: Lesedaten

Datum, Ausgang: Befehl

Befehlsdekodierer:

Eingang: Opcode

Ausgang:

MemToReg

MemWrite

Branch

ALUSrc

RegDst

RegWrite

Ausgang:

ALU-Op

Funktionsdekodierer:

Eingang:

Func

ALUOp

Ausgang

ALU Operation

Datenpfade:

1.) PC (t+1) Ausgang am Befehlszähler geht in Eingang, Leseaddresse vom Befehlsspeicher

2.) Befehslsspeicher, Ausgang, Lesedaten - geht: 31:26 nach Eingang Opcode von Befehsldekodierer

Bit 5:0 geht Eingang Func Funktionsdekodierer

Bit 0:15 (16 Bit) geht Vorzeichenerweiterungseinheit

3.) Vorzeichenerweiterungseinheit

geht 2 Bit Shifter

4.) 2 Bit Shifter geht an Addierer

5.) Addierer geht an MUX

6.) MUX geht Eingang PC (t) in Befehlszähler

PC (t+1) Befehlszähler => Befehlsspeicher => Vorzeichenerweiterungseinheit => 2 Bit Shiter => Addierer => MUX => PC (t) Befehlszähler

1.) PC (t+1) Befehlszähler

2.) Befehlsspeicher

3.) Vorzeichenerweiterungseinheit

4.) 2 Bit Shiter

5.) Addierer

6.) MUX

7.) PC (t) Befehlszähler

3.) Vorzeichenerweiterungseinheit

4.) 2 Bit Shiter

5.) Addierer

3.) Vorzeichenerweiterungseinheit

4.) 2 Bit Shiter

5.) Addierer

6.) MUX

1.) PC (t+1) Befehlszähler

2.) Befehlsspeicher

7.) PC (t) Befehlszähler

Alternative: Befehl inkrementieren

1.) Ausgang PC (t+1) Befehslszähler geht Addierer

Addierer +4

2.) Geht wieder in den Addierer + Vorherigen

3.) Oder in den MUX, direkt in den MUX

4.) Geht in Befehlszähler PC (t)

Also, der erste noch mal:

Datenpfade:

1.) PC (t+1) Ausgang am Befehlszähler geht in Eingang, Leseaddresse vom Befehlsspeicher

2.) Befehslsspeicher, Ausgang, Lesedaten - geht: 31:26 nach Eingang Opcode von Befehsldekodierer

Bit 5:0 geht Eingang Func Funktionsdekodierer

Bit 0:15 (16 Bit) geht Vorzeichenerweiterungseinheit

3.) Vorzeichenerweiterungseinheit

geht 2 Bit Shifter

4.) 2 Bit Shifter geht Addierer, + (Addierer) Geht PC +4 Addierer, alter Befehladdresse +4, von PC

5.) Addierer geht an MUX

6.) MUX geht Eingang PC (t) in Befehlszähler

Befehlsspeicher:

1.) 31:26 geht in Befehlsdekodierer

2.) 5:0 geht in Funktionsdekodierer (Func Feld)

3.) 15:0 16 Bit geht in Vorzeichenerweiterungseinheit

4.) 25:21 geht in Leseregister-1 (Quelloperand)

5.) 20:16 geht in Leseregister-2 (Quelloperand)

6.) 20:16 oder 15:11 geht in MUX geht in Schreiberegister

Da ist ein MUX

20:16 entweder Leseregister-2

Oder - Schreiberegister, wenn Schreiberegister 15:11

1.) 5:0 geht in Funktionsdekodierer (Func Feld)

2.) 15:0 16 Bit geht in Vorzeichenerweiterungseinheit

3.) 20:16 entweder Leseregister-2, 20:16 geht in Leseregister-2 (Quelloperand), 20:16 oder 15:11 geht in MUX geht in Schreiberegister

4.) 25:21 geht in Leseregister-1 (Quelloperand)

5.) 31:26 geht in Befehlsdekodierer

ALU:

Lesedaten-1

Lesedaten-2

Aber bei Lese-Daten-2, MUX

Das MUX kommt von Vorzeichenerweiterungseinheit, 32 Bit von Sprungbefehl

ALU-Ausgang

Geht in Addresse, von Datenspeicher

Oder MUX in Schreibedaten von Registersatz

Echte Datenabhängigkeit: ED

Gegenabhängigkeit: GA

Ausgabeabhängigkeit: AA

I1: addi $t1, $t2, 2

I2: add $t4, $t1, $t3

I3: subi $t3, $t5, 3

I4: subi $t3, $t6, 3

ED: I1, I2

I2 benutzt werden in $t1

der zuvor I1 berechnet wurde

2 x GA:

I2 und I3

I2 und I4

Sowohl I3 und I4 schreiben in $t3

Dass von I2 lesend verwendet wurde

AA:

I3 und I4

Da beide Befehle in das $t3 Register zurückschreiben

Falsche = Scheinbare Datenabhängigkeit = Namensabhängigkeiten = Name Dependency:

Gegenabhängigkeit

Ausgabeabhängigkeit

Sind Datenabhängige Befehle weit voneinander entfernt, so kommt es zu keinem Datenkonflikt

Für einfache Skalare MIPS-Pipeline: Nur echte Datenabhängigkeit von Bedeutung

Superskalar: Auch

Gegenabhängigkeit

Ausgabeabhängigkeit

I1: WB

I2: MEM

I3: EX

I4: ID

I5: IF

IF-Phase: Befehlsregister: Ir

ID-Stufe: ALU-Eingaberegister: Ai1, Ai2

EX-Stufe: ALU-Ausgaberegister: Ao

1.) Wir haben eine Datenabhängigkeit

Diese müssen wir benennen

wir müssen die Datenabhängigkeiten zwischen allen Befehlen benennen, so zu sagen, auch, wenn diese tausend Befehle auseinander liegen

Datenabhängigkeit benennen heisst einfach, zwischen den Befehlen besteht Datenabhängigkeit

Welche Datenabhängigkeit besteht

Das ist einfach so und wir müssen benennen, welche das ist

2.)

1.) Einzyklus

2.) Mehrzyklus

3.) Pipelining

Mehrzyklus heisst,

wir erhöhen den Takt

wir haben viele Stufen

Aber es gibt keine Überlappungen, weil es gibt mehrere Zyklen, aber keine Überlappungen

Beispiel

IF ID EX MEM WB

I1: Schreibt in $t1, WB-Phase

I2: Liesst von $t1, ID-Phase

Mehrzyklus:

I1: 0, IF; 1, ID; 2, EX; 3, MEM; 4, WB (I1 schreibt in $t1)

I2: 5, IF; 6, ID (I2 liesst von $t1); 7, EX; 8, MEM; 9, WB

Pipelining:

I1: 0, IF; 1, ID; 2, EX; 3, MEM; 4, WB (I1 schreibt in $t1)

I2: 0; 1, IF; 2, ID (I2 liesst von $t1); 3, EX; 4, MEM; 5, WB

Jetzt wissen wir - was passiert ist

Wir wissen es gibt Datenkonflikte bzw. Zusammenhänge zwischen Befehlen, egal welche Befehle das sind und egal wie weit sie auseinander liegen

Zwischen I1 und I1023 besteht so oder so eine Datenabhängigkeit egal, ob diese 8192 Befehle auseinander liegen

Bei der Mehrzyklusarchitektur spielt das keine Rolle, weil sie werden immer noch hintereinander abgearbeitet, selbst, wenn mit Zyklen

Die Datenabhängigkeit besteht

Und wir wissen, welche, es gibt 3 verschiedene, GA, GA, GG

Gut:

Mehrzyklus - jetzt können wir sagen, wann sie stattfindet

Der nächste Befehl ist einen Takt später in der Pipeline

Jetzt kommt die Lösung - die ist kein wenig kompliziert - das hat mit Datenflusskonflikten nichts zu tun

Einfügen von Lehrbefehlen durch den Compiler

NOP's

Statische Befehlsumordnung - statt Leerbefehlen, durch bereits vorhandene Befehle

Hardware-Lösung

Leerlauf der Pipeline

I1 und I2: Anhalten des Befehls I2 für zwei Takte, Pipeline-Sperrung, Interlocking

Oder Pipeline-Leerlauf: Stalling

Es entstehen Pipeline-Blasen, Pipeline Bubbles

Die Wirkung ist dieselbe wie bei eingefügten NOP Befehlen

2.) Lösung: Komplizierter: Nimmt das Ergebnis nicht aus Architekturregister sondern von der ALU direkt

Forwarding

Interlocking:

IF, ID, EX, MEM, WB

IF, ID, EX, MEM, WB

0, 1, 2, 3, 4

3, 4, 5, 6, 7

Also: Differenz, immer ein Zyklus

Zwei Befehle Sperren - 2 Zyklen, macht 3

Forwarding: EX->ID

Einzyklus Mikroarchitektur

Mehrzyklus Mikroarchitektur

Pipeline Mikroarchitektur

Einzyklus Mikroarchitektur

Zustandselemente

Datenpfad

Steuereinheit

Vor und Nachteile

Mehrzyklus Mikroarchitektur

Funktionsweise

Vor und Nachteile

Pipeline Mikroarchitektur

Pipeline Prinzip

Stufen der Befehlspipeline

die MIPS-Pipeline

Pipeline-Konflikte

Datenkonflikte und deren Lösungsmöglichkeiten

Steuerflusskonflikte und deren Lösungsmöglichkeiten

Steuerflusskonflikte und Ressourcenkonflikte und deren Lösungsmöglichkeiten

Ausführung in mehrere Takten

zustandselemente

- Befehlszähler

- Befehlsspeicher

- Registersatz

- Datenspeicher

32-Bit-Bus

5-Bit-Bus

PC

- 32 Bit Register

- Wird nach Taktzyklus inkrementiert

- Wird um 4 Inkrementiert

Leseport am Befehlsspeicher

32x32-Bit Registersatz

Zwei lese und Schreibport

5-Bit addressen 2^52 = 32

Datenpfad

Arithmetische und Logische Befehle: R-Typ Befehle

I-Typ-Transportbefehle: lw - Laden eines Wortes

rs-Feld: Befehlswort

rt-Feld: Register Destination

r-Typ-Befehle: add, sub, and, or, slt

Steuereinheit:

- func-Feld

ALUOp

00 Addition

01 subtraktion

10 Nutze das Func-Feld

11 n/a

Func:

- X

- X

- 100 000 - add

- 100 010 - sub

- 100 100 - and

- 100 101 - or

- 101 010 - slt

Dementsprechend die ALU-Operation

Befehl: ALU-OP: 00, x1, 1x - addition direkt, subtraktion direkt

Func Befehl für andere

Dann entsprechend ALU-Operation

ALU-Operation

010 - add

110 - sub

010 - add

110 - sub

000 - and

001 - or

111 - slt - set less than

R-Typ

lw

sw

beq

Pipelining:

- Kritischer Pfad: Schaltnetz mit der längsten Verzögerungszeit

- Latenz: Ist die Anzahl der Takte, die ein Befehl braucht um die gesamte Pipeline zu durchlaufen

- Durchsatz: Anzahkl der Befehle, die pro Takt, die Pipeline verlassen können

Beschleunigung, Speeadup

Stufen

Pipelnie Konflikte

Piplene Hemmnisse Hazards

Datenkonflikte

steuerflusskonflikte

Struktur und Ressourcenkonflikte

Datenabhängigkeit zwischen Befehlen I1 und I2

Echte Datenabhängigkeit: RAW - Read After Write - True Dependency

Gegenabhängigkeit: WAR - Write after Read - Anti Dependency

Ausgabenabhängigkeit: WAW - Schreibe nach Lese Konflikt

Abhängigkeitsgraph

falsche bzw. scheinbare Datenabhängigkeit

Namensabhängigkeiten - Name Dependency

Integrationsdichte Kurzbezeichnung Anzahl Transistoren

Small Scale Integration SSI 100

Medium Scale Integration MSI 1.000

Large Scale Integration LSI 10.000

Very Large Scale Integration VLSI 100.000

Ultra Large Scale Integration ULSI 1.000.000

Super Large Scale Integration SLSI 10.000.000

Extra Large Scale Integration ELSI 100.000.000

Giga Scale Integration GSI > 1.000.000.000

Strukturbreite: 10 Mikro Meter bis 0.01 Mikro Meter

Intel Xeon 22-Core Xeon Bradwell E5

Maskenprogrammierbar: ASIC

Elektrisch Programmierbar: FPGA

Pipelining: Überlappende Befehlsverarbeitung

CISC, RISC

EPIC: Explicitly Parallel Instruction Computing: Mischung aus RISC und CISC

Befehlssatzarchitektur: Instruction Set Architecture ISA: definiert die Grenze zwischen Hardware und Software

Befehlssatzarchitektur = Prozessoarchitektur = Programmiermodell

Prozessorarchitektur keine Aussagen über Detail der Hardware

Mikroarchitektur: Implementierung des Prozessors

Prozessortechniken: Mikroarchitektur, Prozessoarchitektur

binärkompatibel

Prozessorfamilie: Gleiche Basisarchitektur

1.) Register und Speichermodell

2.) Datenformate

3.) Befehlssatz

4.) Befehlsformate

5.) Addressierungsarten

Addressraumorganisation

Architekturregister: Vom Programmierer ansprechbare Register

Allgemeine Register, Multimediaregister, Gleitkommaregister, Spezialregister

b: Byte

h: Halbwort (16 Bit)

w: Wort (32 Bit)

d: Doppelwort (64 Bit)

logischer Addressraum

1.) Programmcode Statische Daten

2.) Dynamische Daten (Heap)

3.) Laufzeitstapel (Stack)

4.) Bereich für E/A

aligned: Big-Endian, Little-Endian

Lerne den Spruch: Little-Endian ist falsch rum, Big-Endian ist richtig rum

SSL - Shift Logical Left

SLR - Shift Logical Right

SAR - Shift arithmetic Right

ROL - Rotate Left

ROR - Rotate Right

1.) Befehlssatz

2.) Befehlsformate

Befehlsformate

operaion code

instruction format

1.) Dreiaddressformat: opcode - dest - src1 - src2

2.) Zweiaddressformat: opcode - dest/src1 src2

3.) Einaddressformat: opcode - src

4.) Nulladdressformat: opcode

Quell-Operanden: src1, src2

Zieloperand: dest

Lade- und Speicherarchitektur: Nur Lade und Speicherbefehle transportieren Daten zwischen dem Hauptspeicher und den Registern

Register-Speicher: Mindestens eines ist Register eines ist Speicher

Einaddressbefehle: Akkumulatorarchitektur

Speicher-Speicherarchitektur: Einziger: TI 9900 Texas Instruments

Befehle: load, store, sub, add

Registeraddressierung: Opcode Registerbezeichner RegisterBezeichner RegisterBezeichner

Unmittelbare Addressierung: Opcode Operand

Direkt oder Absolut: Opcode RegisterBezeichner Speicheraddresse

Registerindirekte Addressierung mit Verschiebung: Opcode Registerbezeichner Verschiebung

Befehlszählerrelativ

Registeraddressierung: Opcode Registerbezeichner RegisterBezeichner RegisterBezeichner

Registerbezeichner 2 zeigt auf Registersatz

Unmittelbare Addressierung: Opcode Operand

Direkt oder Absolut: Opcode RegisterBezeichner Speicheraddresse

Speicheraddresse zeigt Auf Speicher

Registeraddressierung: Opcode Registerbezeichner RegisterBezeichner RegisterBezeichner

Registerbezeichner 2 zeigt Registersatz zeigt auf Operand im Speicher

Registerindirekte Addressierung mit Verschiebung: Opcode Registerbezeichner Verschiebung

Indizierte Addressierung: OpCode Registerbezeichner

Befehlszählerrelativ

Register load R1, R2

Unmittelbare load R1, const

direkt, absolut load R1, (const)

registerindirekt load R1, (R2)

Postinkrement load R1, (R2)+

Prädekrement load R1, -(R2)

registerindirekt mit

Verschiebung load R1, displ(R2)

Indiziert load R1, displ(R2,R3)

Befehlszählerrelativ branch displ

MARS: MIPS Assembler and Runtime Simulator

Register: $zero,

$at,

$v0 - $v1,

$a0 - $a3,

$t0 - $t9,

$s0 - $s7,

$k0 - $k1,

$gp,

$sp,

$fp,

$ra

R-Typ-Befehle

I-Typ-Befehle

J-Typ-Befehle

R-Typ

I-Typ

J-Typ

R-Typ: op rs rt rd sa func

I-Typ: op rs rt immediate

J-Typ: op target address

R-Typ:

op

rs

rt

rd

sa

func

I-Typ:

op

rs

rt

immediate

J-Typ:

op

target

address

R-Typ:

op 31 bis 26

rs 25 bis 21

rt 20 bis 16

rd 15 bis 11

sa 10 bis 6

func 5 bis 0

I-Typ: op rs rt immediate

op 31 bis 26

rs 25 bis 21

rt 20 bis 16

immidiate 15 bis 0

J-Typ:

op 31 bis 26

target address 25 bis 0

Quell und Zielregister:

rs

rt

rd

Unmittelbarer Operand

immidiate

Verzweigungsaddresse

target address

Verschiebewerte

sa

move

mov.s Transport zwischen Universalregistern

mov.d Transport zwischen Gleitkommaregistern

mfhi, mflo Transfer zwischen Universalregister und Register Hi und Lo

mthi, mtlo

mfc1, mtc1 Transfer zwischen Universalregistern und Gleitkommaregistern

sll, sllv Logische Linksverschiebung

srl, srlv Logische Rechtsverschiebung

sra, srav Arithmetische Rechtsverschiebung

rol, ror Rotation links bzw. rechts

slt, slti, sltu, sltiu Vergleich kleiner

sgt, sgtu Vergleich gleich bzw. ungleich

sge, sgeu Vergleich grösser gleich

sle, sleu Vergleich kleiner gleich

I-Typ-Transportbefehl: Laden eines wortes - lw

1.) Inhalt des Quellregisters auslesen:

Basisaddresse für die Bestimmung der Zieladdresse im Datenspeicher

Quellregister: rs-feld

Vorgang: Befehlszähler -> Befehlsspeicher -> Registersatz (Lese-Register-1, Lese-Daten-1) -> Datenspeicher

2.) lw: Offset

Unmittelbare Feld des Befehlswortes (Befehle [15:0])

Datenpfad: Befehlszähler -> Befehlsspeicher -> Vorzeichenerweiterungseinheit -> ALU -> Datenspeicher

Und: Befehlszähler -> Befehlsspeicher -> Register-Satz -> Lese-Daten-1 -> ALU -> Addresse, Datenspeicher

ALU: Immidiate + Lese-Daten-1

3.) Lese-Daten von Datenspeicher -> Schreibedaten, Schreiberegister von Registersatz

rt-Feld: Register Destination

Befehlswort (Befehl [20:16])

Steuersignal: RegWrite: WE - Am Registersatz

4.) Schritt: Addresse des nächsten Befehls:

PC (t) -> Addierer + 4 -> PC (t+1)

Datenpfad - zum Speichern eines Wortes

sw

in den Datenspeicher geschrieben: rt-Feld Befehl[20:16]

WE-Port des Datenspeichers: MemWrite

MemWrite

RegWrite

Kontrolle des Multiplexers: ALU-Src